Marvell Ethernet Switches and Routers with SONiC for Optimal Open Networking Performance in Asterfusion

written by Asterfuison

Table of Contents

Introduction

In the AI-driven era, network infrastructure is confronting practical challenges. Within artificial intelligence (AI) and machine learning (ML) scenarios, the demand for network bandwidth generated by data interaction keeps growing, while the requirement for latency becomes increasingly stringent — these factors directly drive the upgrade of network architecture from cloud to edge. During this process, the bottleneck of network performance is gradually converging on the technical capabilities of underlying hardware, namely Application-Specific Integrated Circuits (ASICs).

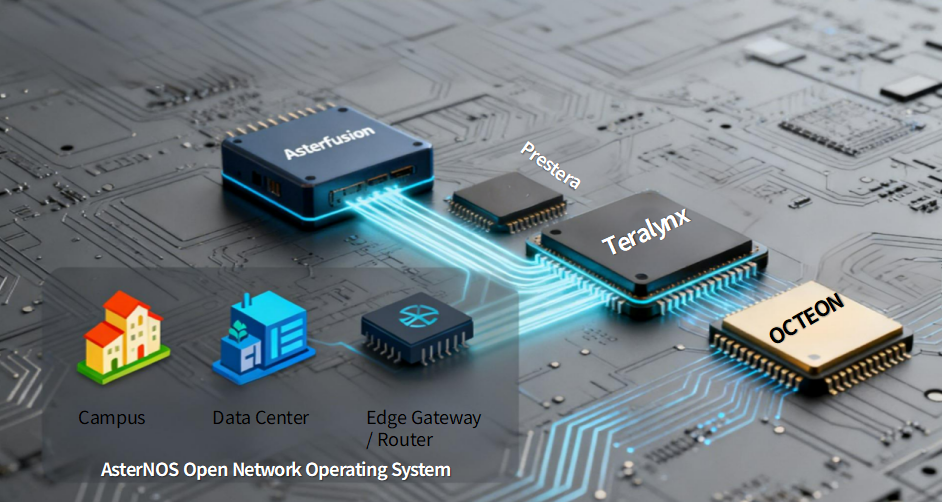

Marvell boasts mature technologies in the field of high-performance network chips, and its Marvell Ethernet Switches-based ASIC solutions serve as a crucial underpinning for addressing current network demands. Looking across Asterfusion’s three major product lines — campus, data center, and edge gateway routers — its self-developed AsterNOS open network operating system forms effective collaboration with the three core chip product lines under Marvell’s open network ASIC architecture. These three chip product lines have clear divisions of labor:

- Prestera (including Falcon, Aldrin2/3, and AlleyCat 5X/5Y) focuses on basic switching functions;

- Teralynx specializes in high-speed switching scenarios;

- OCTEON is responsible for intelligent data processing.

The three work in synergy to support a complete open network system covering the access layer → aggregation layer → core layer → intelligent edge, with Marvell Ethernet Switches acting as the core hardware foundation throughout the system in Asterfusion.

Ⅰ. Marvell OCTEON with AsterNOS-VPP for Open Gateway Router & DPU

This section focuses on routers and DPU (Data Processing Unit) platforms, which adopt Marvell’s OCTEON series chips. The OCTEON series is positioned as a high-performance, multi-core, programmable intelligent processing platform, suitable for 5G, cloud computing, enterprise networks, and security/monitoring applications.

- OCTEON 10 (CN102/CN103) – Router

OCTEON 10 (CN102/CN103) is equipped with 8 ARM64 Neoverse N2 cores, supports DDR5 memory expansion, and integrates a dedicated routing acceleration engine. It enables hardware offloading for tasks such as IPv4/IPv6 forwarding and BGP protocol processing, preventing unnecessary CPU resource consumption.

Unlike switching chips, OCTEON 10 does not take high-port-density switching as its primary goal; instead, it focuses on routing. Asterfusion delivers routing capabilities through the “AsterNOS+VPP” architecture — AsterNOS (developed based on SONiC) handles routing protocol configuration and device management in the control plane, while VPP (Vector Packet Processing) runs on ASIC hardware to accelerate packet forwarding in the data plane. With forwarding latency as low as the microsecond level, it enables high-performance, programmable white-box routing.

- OCTEON TX2 (CN9670) – DPU/SmartNIC

OCTEON TX2 (CN9670) provides 24-48 core ARM64 CPUs, integrates PCIe Gen4 interfaces and hardware encryption engines, and supports “non-forwarding intelligent tasks” such as virtualization offloading, security processing, and data compression. Its core purpose is to “reduce the load” on servers — transferring network tasks that were originally handled by the CPU to DPU hardware.Compared with OCTEON 10 (designed for routers), OCTEON TX2 focuses more on “service offloading” rather than routing and forwarding. For example, in cloud computing scenarios, it can offload tasks such as KVM virtualized network I/O, VXLAN tunnel encapsulation/decapsulation, and IPsec encryption to hardware, reducing server CPU utilization.

Ⅱ. Marvell Teralynx & Prestera powering Ultra Scale Data Center

The Asterfusion Data Center (DC) product line is mainly driven by Marvell’s Teralynx series and part of the Prestera (Falcon) series chips, — key components of Marvell Ethernet Switches — which are designed for cloud computing and AI/HPC environments requiring high throughput and low latency.

Teralynx 7 : Balanced Performance for Data Center Spine Layers

It covers a switching capacity of 3.2-12.8 Tbps, supports 100G/200G/400G ports, and has a stable latency of ~500ns. Asterfusion products support 9216-byte Jumbo Frames, which can reduce the number of packet fragmentations and improve the efficiency of large-file transmission.

Compared with the Prestera series, the core difference of Teralynx 7 lies in “speed and latency” — the 32×400G ports of CX732Q-N support a single-port speed of 400G, which is 4 times that of Prestera Falcon 2.0T (maximum 100G); the ~500ns latency is more than 60% lower than the ~1400ns of Falcon 2.0T, making it more suitable for RDMA traffic forwarding in AI training clusters.

Asterfusion Product Mapping: CX532P-N, CX564P-N, CX664D-N, CX732Q-N

Teralynx 10: Flagship Chip for Next-Gen AI Data Centers

The switching capacity of Teralynx 10 jumps to 51.2 Tbps, supporting multi-rate ports of 800G/400G/200G/100G (a single device supports up to 512×100G ports). The cut-through latency is only 560ns, and it integrates the FASTER architecture (Terabit Ethernet Router Slicing), which can simplify network layers and reduce total cost of ownership (TCO).

As the flagship model of the Teralynx family, its core difference from Teralynx 7 lies in “capacity and forward-looking capabilities” — the 51.2 Tbps switching capacity is 4 times that of Teralynx 7 (12.8 Tbps). The 800G ports support high-speed access for next-generation servers, which can meet the traffic demands of ultra-large-scale AI data centers (such as kilocalorie GPU clusters), solidifying its role as the future infrastructure of Marvell Ethernet Switches for next-generation AI/ML and ultra-large-scale cloud networks.

Prestera (Falcon) 2.0T: Reliable ToR Access for Data Centers

The Prestera Falcon chip—used in CX308P-48Y-N-V2—belongs to the Prestera series. It is a key choice for the data center ToR (Top of Rack) access layer, thanks to enhanced routing capabilities like 288,000 IPv4 Prefixes and 144,000 IPv6 Prefixes.

It has a throughput of 2.0 Tbps, a forwarding capacity of 2.8 Bpps, and supports PTP (Precision Time Protocol) —— which enables its application in time-sensitive scenarios.

Asterfusion Product: CX308P-48Y-N-V2

The following table presents the hardware specifications and key features of all AIDC switches:

| Model | Hardware Specifications | Focus On | PTP | Software Features |

| CX308P‑48Y‑N‑V2 | 48 × 25G SFP28 8 × 100G QSFP28 Marvell Falcon | enhanced routing capacity: IPv4: 288,000 Host + 288,000 Prefix IPv6: 144,000 Host + 144,000 Prefix | Supports IEEE 1588v2 PTP (TC / BC modes) | Pre-installed Enterprise SONiC; Supports L2/L3 routing (BGP, OSPF, etc.), VLAN, LAG/MC-LAG, EVPN/VXLAN, RoCEv2, INT (for latency-sensitive scenarios) |

| CX532P‑N | 32 × 100G QSFP28 2 × 10G SFP+ Marvell Teralynx 7 | Latency: 500ns | Not supported | Pre-installed Enterprise SONiC; Supports RoCEv2, EVPN/VXLAN/EVPN Multihoming, L2/L3, ECMP, MC-LAG |

| CX564P‑N | 64 × 100G QSFP28 2 × 10G SFP+ Marvell Teralynx 7 | Latency: 500ns | Not supported | Pre-installed Enterprise SONiC; Supports RoCEv2, EVPN Multihoming, VXLAN, BGP/OSPF, INT, automation, and virtualization features |

| CX664D‑N | 64 × 200G QSFP56 Marvell Teralynx 7 | Latency:~500ns | Not supported | Pre-installed Enterprise SONiC; Supports RoCEv2, EVPN/VXLAN/EVPN Multihoming, L2/L3 advanced features, automation, and network visualization |

| CX732Q‑N | 32 × 400G QSFP-DD Marvell Teralynx 7 | Latency: 500ns | Not supported | Pre-installed Enterprise SONiC; Supports RoCEv2, EVPN/VXLAN/EVPN Multihoming, BGP-EVPN Multihoming, virtualization, automation, and advanced network features |

| CX864E‑N | 64 × 800G OSFP; supports 128×400G / 256×200G / 512×100G interfaces; Marvell Teralynx 10 | Cut-through latency: 560ns | Supports high-precision PTP / SyncE | Pre-installed Enterprise SONiC; Supports RoCEv2, EVPN Multihoming, BGP-EVPN, VXLAN, multi-protocol EVPN, automation, open APIs (REST / gNMI / NETCONF) |

For more comprehensive details, refer to the full article: Powerful Marvell Teralynx and Falcon Chips in Asterfusion Data Center Switches

Ⅲ. Marvell Prestera Series: Enterprise-Grade Access & Aggregation Layer Chips

The Marvell Prestera series is a pillar product of Marvell, a core part of Marvell Ethernet Switches, and serves as the core of “general-purpose switching”. It covers the access layer and aggregation layer of enterprise campuses and medium-to-small data centers. Through sub-series such as AlleyCat, Aldrin, and Falcon, it achieves differentiated adaptation ranging from 1G to 100G speeds, and from simple access to complex aggregation scenarios.

Falcon: “Performance Supplement” for High-End Campuses and Data Center ToR

It is designed for ultra-high performance and reliability. Models built on this chipset deliver a switching capacity of 2.0T–3.2T, supporting 48×25Gb downlink ports and 100Gb / 400Gb QSFP-DD uplink ports. Model design includes hot-swappable PSUs and fans, ensuring stable 24/7 operation.

It supports 504K IPv4 and 252K IPv6 routes, enabling it to meet the needs of both high-end campus core scenarios and Top of Rack (ToR) scenarios in medium-to-small data centers.

For detailed specifications, please refer to Falcon 2.0T (Prestera 98CX85xx)

Prestera Series (Aldrin3/Aldrin2): Flexible Campus Aggregation with 5G Readiness

It supports 10G/25G/100G ports, integrates VXLAN tunnel encapsulation capabilities, and enhances security functions (such as IP Source Guard). Some models (Aldrin3, 98DX7332) support PTP and SyncE synchronization, adapting to the “multi-access + security + flexible networking” requirements of the campus aggregation layer.

For scenarios requiring 5G fronthaul, latency sensitivity, network slicing, or time synchronization, Prestera Aldrin3 has more advantages, as this product excels in these aspects and explicitly supports Class C PTP, SyncE, and more; while for campus LAN, access, or relatively traditional enterprise network use cases, Prestera Aldrin2 is sufficient and offers better cost-effectiveness.

Prestera Series (AlleyCat5Y/AlleyCat5X): Cost-Effective Access for Terminal-Dense Scenarios

It focuses on 1G/2.5G/5G/10G multi-rate ports, integrates PTP IEEE 1588v1/v2 time synchronization function, features low power consumption and controllable cost, and is suitable for terminal-dense access scenarios.

Compared with Aldrin and Falcon in the same family, the core difference of AlleyCat lies in “speed and function simplification”, delivering better cost-effectiveness. Therefore, it is more suitable for terminal access rather than core aggregation.

Additionally, it has a built-in advanced PTP function, which delivers nanosecond-level time synchronization accuracy.

In addition, this series centers on the enterprise SONiC ecosystem. Paired with the OpenWiFi Controller, it enables centralized management covering wired and wireless networks, as well as devices from APs, leaf switches, spine switches to routers. Users can monitor the entire network status via a single interface, reducing overall O&M costs.

In terms of business support, it fully supports network virtualization technologies including VXLAN and BGP EVPN, along with multicast Multicast VXLAN. It also comes with MPLS functionality.

The following is a summary of chip sub-series features from table data, highlighting hardware/software functions and scenario adaptability for quick comparison:

| Chip Sub-series | Hardware Features | Representative Product Models | Software Features (Base) | Optional |

| Falcon | 1. Switching capacity up to 2.0 – 3.2Tbps; 2. Supports 25G/100G/400G ports, available in 24-48 ports; 3. Boasts 504K and 252K large enhanced routing table entries for IPv4 and IPv6 respectively; 4. Functions as core/spine switch | CX732Q-M-H CX532P-M-H CX308P-48Y-M-H | 1. Network virtualization technologies, e.g., VXLAN, BGP-EVPN, Multicast VXLAN; 2. High availability and scalability, e.g., EVPN Multihoming, MLAG | Optional PTP and MPLS Optional Dual OCTEON DPUs |

| Aldrin3 | 1. Supports 10G/25G/100G ports; 2. Functions as aggregation layer/leaf switch | CX202P-24Y-M-H CX204P-16Y-M-E | 1. Equipped with VXLAN tunnel encapsulation capability and BGP-EVPN; 2. Features enhanced terminal access security functions like IP Source Guard; 3. High availability and scalability, e.g., MLAG; 4. MACsec supported on selected models | Optional PTP and MPLS |

| Aldrin2 | 1. Supports 10G/25G/100G ports; 2. Configurable as leaf and aggregation switches | CX206P-48S-M-H CX202P-24S-M-H | 1. Equipped with VXLAN tunnel encapsulation capability and BGP-EVPN; 2. Features enhanced terminal access security functions like IP Source Guard; 3. High availability and scalability, e.g., MLAG; | Optional PTP and MPLS |

| AlleyCat5X | 1. Focuses on 1G/2.5G/5G/10G multi-rate ports; 2. Supports 10G/25G multi-rate uplinks; 3. Cost-effective, designed for access layer switches | CX206Y-48MT-M-HPW8 CX206Y-48GT-M-HWP8 | 1. Equipped with VXLAN tunnel encapsulation capability and BGP-EVPN; 2. Basic routing protocols: OSPF, BGP; 3. High availability, e.g., MLAG, EVPN Multihoming; 4. Features enhanced terminal access security functions like IP Source Guard; 5. Supports POE+ / POE++ | Optional PTP and NPB |

| AlleyCat5Y | 1. Focuses on 1G/2.5G/5G/10G multi-rate ports; 2. Mostly used for 10G uplinks; 3. Cost-effective, designed for access layer switches | CX102S-8MT-M-SWP CX102S-16GT-M-SWP | 1. Basic routing functions: OSPF and BGP; 2. High availability, e.g., MLAG; 3.Features enhanced terminal access security functions like IP Source Guard;4 . VXLAN and BGP-EVPN not supported on selected models;5. Supports POE+ / POE++ | Optional PTP and NPB |

After learning about Asterfusion devices, you may notice an interesting pattern: we offer similar types of switches for both AIDC and campus networks.

For example, the CX308P-48Y-M-H for campus and the CX308P-48Y-N-V2 for AIDC.

How should you choose between them?

Let’s first examine a functional comparison.

| Comparison | CX308P-48Y-M-H | CX308P-48Y-N-V2 |

| Target Scenario | Campus network aggregation/core, Spine/Leaf for small-to-medium data centers | ToR (Top of Rack)/Leaf for large-scale data centers |

| Core Chip | Marvell Falcon 2.0T ASIC | Marvell Falcon 2.0T ASIC |

| Operating System | AsterNOS Campus Edition | AsterNOS AIDC Edition |

| Forwarding Performance | 2.8 Bpps | 2600 Mpps (tested with small packets) |

| Routing Table Entries | IPv4: 504KIPv6: 252K | IPv4: 288K host + 288K prefixIPv6: 144K host + 144K prefix |

| MAC Table Entries | 32K | 128K |

| Key Features | MPLS, PTP, OpenWiFi controller integration | RoCEv2 (lossless network), INT telemetry, PTP |

| Focus Areas | Forwarding capability, large routing table | Ultra-low latency, large routing table |

| Multicast Support | Yes (including Multicast VXLAN) | No |

| Visualization Requirement | No | Yes (Prometheus + Grafana integration) |

| Reliability | MC-LAG | MC-LAG, EVPN-Multihoming |

By comparing the specifications in a table, you can clearly select the device that meets your requirements. Both models come preloaded with Enterprise SONiC, but the N series differs in OS features, routing table capacity, and traffic visualization capabilities.

In general, for enterprise network core or aggregation layers, or scenarios requiring MPLS line support and simplified operations, the CX308P-48Y-M-H is recommended. For large data center server-side deployments that require traffic visualization, AI computing support, and granular routing table management (host routes and prefix routes), the CX308P-48Y-N-V2 is more suitable.

Similarly, for other series such as CX532P-M-H / CX732Q-M-H and CX532P-N / CX732Q-N, the selection logic is the same and can be based on port type and speed requirements.

If you are unsure or have any questions, you can contact our experts for a detailed assessment and network architecture design by clicking here.

Ⅳ. Marvell Ethernet Switches & Router Comparison: Matching Asterfusion Products to Use Cases

Within the Asterfusion product portfolio, the value of Marvell chips is demonstrated as follows:

- Campus Series (Access/Aggregation Layer): Adopts AlleyCat5X / 5Y / Aldrin2 / Aldrin3— core chips of Marvell Ethernet Switches —to match different bandwidth requirements. It also uses Falcon 2.0T and 3.2T as high-end core/spine switching devices.

- Data Center Series (Core/ToR Layer): Employs Falcon / Teralynx7 / Teralynx10, designed for high throughput and low latency scenarios.

- Router Series: Equipped with Marvell OCTEON DPU (CN102/CN103), responsible for separating control plane and data plane.

- DPU Platform: Utilizes OCTEON TX2 CN9670, adapted to the FusionNOS framework for upper-layer service deployment and function acceleration.

To better illustrate the differences among Marvell’s three chip families, we compare them across four dimensions—with reference to Asterfusion products.

| Chip Family | Core Capabilities | Port Speed Range | Focus On | Core Scenarios | Representative Asterfusion Products | Key Functional Differences |

| OCTEON | Intelligent Processing (Routing/DPU) | 10G/100G | High-Performance Data Processing Routing and Security | Routers, Edge DPU | ET2508 (Routing), ET3212A (DPU) | Control + data plane separation; supports routing protocols / service offloading |

| Teralynx | High-Speed Switching | 100G/200G/400G/800G | Low Latency: ~500ns-560ns | AI Data Center Core/Aggregation | CX732Q-N (400G), CX864E-N (800G) | Ultra-high switching capacity (up to 51.2Tbps); low latency; supports Jumbo Frame |

| Prestera-Falcon | High-End Campus/DC ToR | 25G/100G | Enhanced routing table items | Campus Core, DC ToR, O-RAN Fronthaul | CX308P-48Y-N-V2, CX306P-48Y-M-H | High port density; supports O-RAN time synchronization |

| Prestera-Aldrin | Campus Aggregation | 10G/25G/100G | Medium/High-Speed Port Adaptation Basic Network Virtualization Capability | Campus Aggregation Layer | CX202P-24Y-M-H, CX206P-48S-M-H | Supports VXLAN/EVPN and MC-LAG; enhanced security features |

| Prestera-AlleyCat | General-Purpose Access | 1G/2.5G/5G/10G | Cost Control Multi-Rate Access | Campus Access Layer | CX102S-8MT-M-S, CX204Y-24GT-M-S | Multi-rate adaptation; basic security; cost-effective |

Ⅴ. Conclusion

By integrating the three major chip families of Prestera (Falcon, Aldrin 2/3, AlleyCat 5X/5Y) , Teralynx and OCTEON— the hardware core of Marvell Ethernet Switches & Routers — Asterfusion has built a complete network solution covering from access layer, aggregation layer to core layer and intelligent edge. Whether for campus networks, enterprise cores or ultra-large-scale data centers, the combination of Marvell chips and AsterNOS/AsterNOS-VPP can deliver a high-performance, low-latency, programmable and secure network experience.

On this basis, Asterfusion further integrates scattered hardware capabilities into a unified and manageable network system through OpenWiFi Controller, network visualization and automation tools — whether it is dynamic isolation of campus tenants, low-latency transmission of data center GPU clusters, or virtualization offloading of edge nodes, all can be efficiently adapted through the “Marvell chips + AsterNOS” combination.

In the future, with the popularization of 400G/800G ports and the continuous growth of AI computing power demand, Asterfusion will continue to deepen cooperation with Marvell’s open network ASIC architecture, promote technical iterations based on the existing product matrix, and provide enterprises with full-lifecycle network solutions from “hardware selection” to “system deployment” and then to “long-term operation and maintenance”.

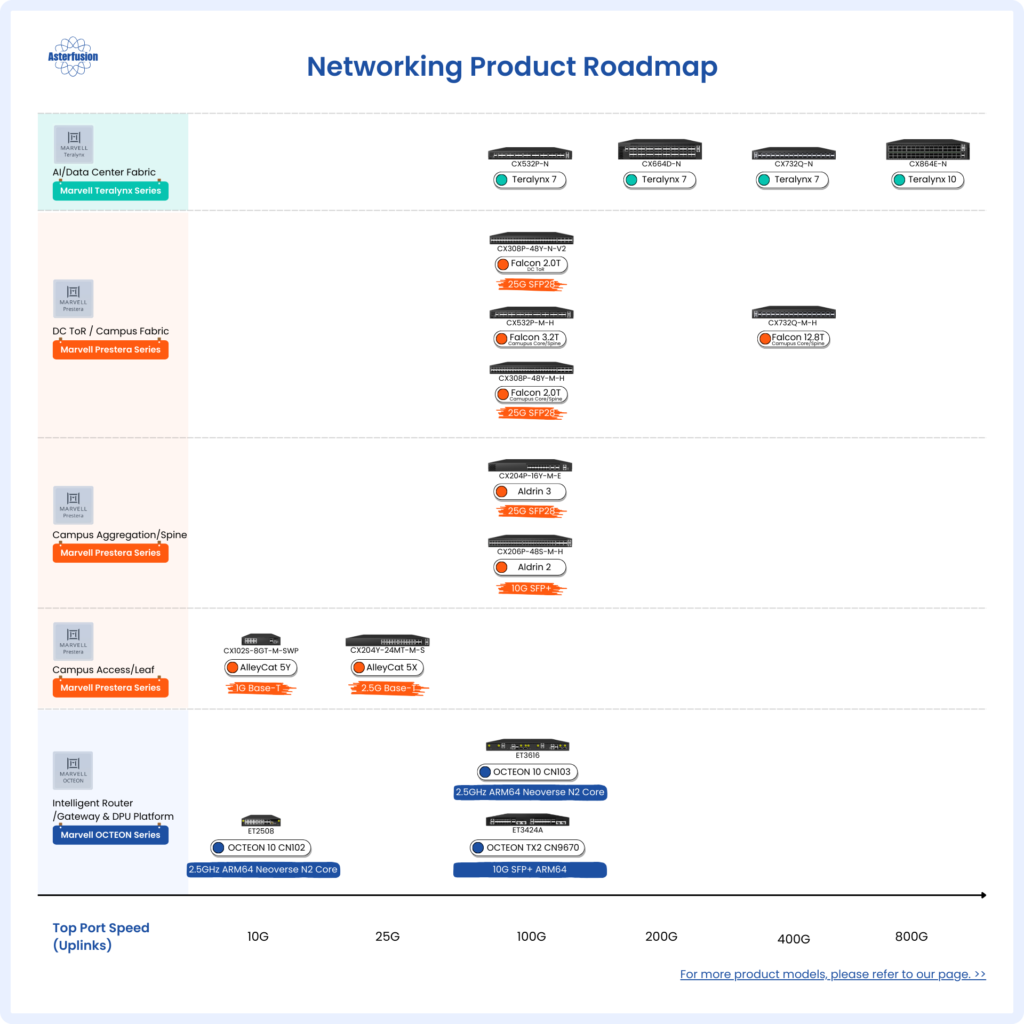

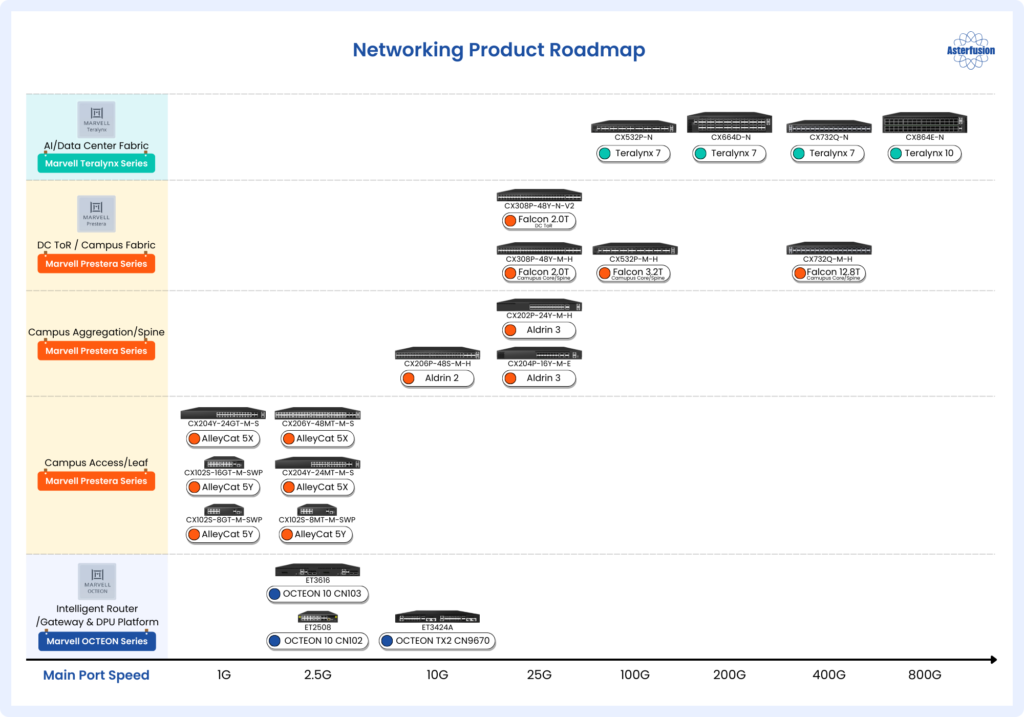

Asterfusion Product Roadmap

The above picture showcases Asterfusion products, including intelligent edge routers/DPU platforms, data center low-latency switches, and campus aggregation/access switches, arranged by main port speed from 1G Base-T to 2.5G Base-T, and from 10G SFP to 800G OSFP. Only one device is shown as a representative.

For more products, please visit our product page or contact us.